Moderní výrobní procesy: trubkovité tranzistory přichází

16.6.2017, Jan Vítek, článek

IBM se chystá spustit další revoluci ve výrobních procesech čipů, a to podobnou, jakou si připravil Intel při představení prvních tranzistorů Tri-gate před šesti lety. Tehdy ještě šlo o 22nm technologii, která zajistila jeho náskok, ale nyní už jde o 5 nm.

Kapitoly článku:

Zatímco technologie EUV má přijít kvůli tomu, aby výrobci mohli vytvářet čím dál menší struktury včetně tranzistorů, technologie GAA bude zase sloužit tomu, aby tyto tranzistory mohly fungovat efektivně.

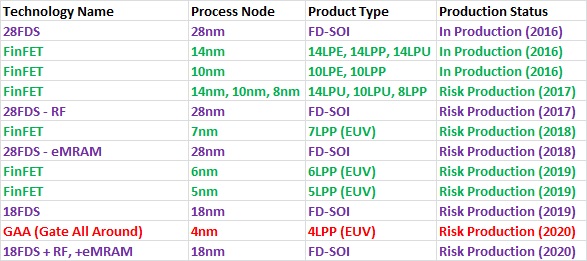

O tranzistorech GAA jsme se dozvěděli teprve nedávno, a to z prezentace firmy Samsung, která se pochlubila, že je chce využít ve své 4nm technologii. Tehdy ještě nebylo vůbec jasné, o co má jít, ale lecos napovědělo právě vysvětlení zkratky GAA - Gate All Around.

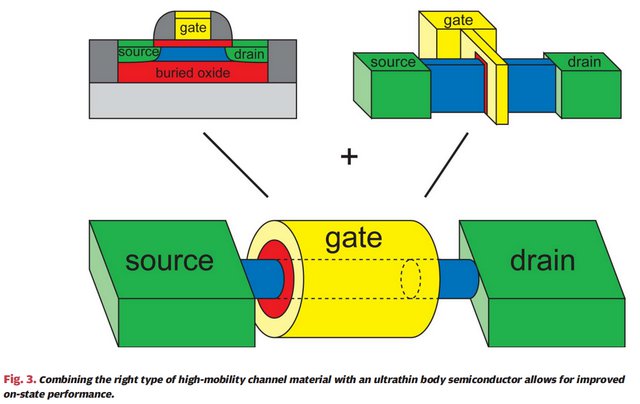

Bylo tak zřejmé, že v jejím případě bude hradlo tranzistoru obklopovat už celý kanál, čímž se maximalizuje prostor pro průchod elektronů. Poté jsme se díky prezentaci firmy IBM už mohli podívat, jak tyto tranzistory budou vypadat a jaké je jejich schema.

Obrázek ukazuje 3 typy tranzistorů, přičemž nalevo nahoře je klasický typ rovinného či plochého tranzistoru, nahoře vpravo máme aktuální FinFET s vertikálně narostlým kanálem v hradlu a dole je zbrusu nový GAA tranzistor (čili GAAFET) s trubkovitým hradlem (gate). Jde právě o maximalizaci plochy mezi ním a modrým kanálem, kterou zvýrazňuje červená barva. Právě tudy budou při zapnutém stavu proudit elektrony a pokud máme zájem o co největší výkon takového tranzistoru, potřebujeme, aby tato plocha byla co největší.

A jak ukazuje fotografie samotných GAAFET nahoře, tyto kanály vedoucí skrz bránu mohou být třeba tři. Jak jsme uvedli v druhé kapitole o 22nm procesu Intel a prvních tranzistorech Tri-gate, i v tomto případě byly tranzistory tvořeny v případě potřeby se třemi kanály v podobě vertikálních žeber. Ty už ale musely být uloženy vedle sebe, zatímco ve struktuře GAA mohou být přímo nad sebou, což má za logický následek vyšší hustotu tranzistorů, i když trojnásobek to rozhodně není.

IBM připravilo také menší srovnání GAAFET s FinFET. Jak je vidět, vychází se z efektivity (Weff) FinFET, která je u něj na základní hodnotě 1 a v různých designech GAAFET se může dojít až na hodnotu 1,3 při stejné horizontální ploše, kterou tranzistor zabere.

A jakým způsobem se GAAFET vyrábí? To ukazuje tato koláž, dle níž se nejdříve položí napřeskáčku vrstvy křemíku a sloučeniny křemíku a germania (SiGe). Právě SiGe poslouží jako podpůrná struktura, která se odstraní technikou Atomic Layer Etching a vzniknou tzv. nanosheet, čili nanovrstvičky křemíku. Volný prostor je pak zaplněn High-K dielektrikem, což není zrovna lehký úkol, který v IBM dle svých slov vyřešili s využitím speciálních chemikálií a techniky ALD - Atomic Layer Deposition.

Tranzistory GAA nejsou ale jedinou možnou náhradou FinFET. Jak ukazuje zase tento obrázek, možné jsou 3 cesty, přičemž ta vrchní počítá právě s GAA, které jsou naznačeny ve vertikální, ne horizontální poloze. Jak dobré jsou ale dle IBM GAAFET?

Firma se snaží srovnávat s tím nejlepším, co je na trhu a uvádí, že oproti 10nm technologii FinFET umí 5nm GAAFET nabídnout o 40 % vyšší výkon tranzistorů při stejném napětí nebo o 75 % nižší spotřebu při stejném výkonu. Jde ale především o hustotu uložení tranzistorů. Už jsme se dozvěděli, co IBM myslí oním čipem o velikosti nehtu, na který dokáže uložit 30 miliard tranzistorů, zatímco 7nm technologie jich zvládne 20 miliard.

Jde o čip o velikosti 50 mm2, takže si to s něčím srovnejme. Přímo na ráně jsou moderní GPU, a to třeba 16nm NVIDIA GP106 s velikostí 200 mm2 a počtem tranzistorů "pouze" 4,4 miliard jako veskrze průměrné GPU na dnešní dobu. Kdyby však šlo o 5nm čip s tranzistory GAA vytvořenými pomocí EUV, pak by dle prostého výpočtu mohl mít až 120 miliard tranzistorů, což samozřejmě nelze brát jako hotovou věc. Monstrózní GV100 generace Tesla je už vyrobena z 21 miliard tranzistorů 12nm procesem, čili dnes se zvládají vyrábět i podstatně komplikovanější čipy než GP106, ale GV100 také zabírá plochu 815 mm2.

Vypadá to, že se na svět klubají technologie, které umožní výrobcům procesorů, grafických čipů a jiného hardwaru se teprve pořádně vyřádit. A to se ještě můžeme brzy dozvědět o dalších novinkách, jako je pokrok ve vrstvení počítačových čipů, kde jsou nejdále zatím výrobci pamětí NAND Flash.

450mm wafery nebudou

V minulosti počítačový průmysl sázel ve snaze o připravení ještě masovější a levnější výroby počítačových čipů na větší a větší wafery. Jak je dobře známo, to jsou křemíkové desky nařezané z válců vysoce čistého křemíku, které slouží jako základ pro počítačové čipy. Platí zde přitom, že čím větší wafer je, tím více čipů se z něj dá výsledným rozřezáním získat.

Je tak zřejmé, že cílem výrobců bylo využívat co největší wafery, ale to pochopitelně nejde zařídit snadno. Je jasné, že tu jsou i nevýhody, a to především nutnost přejít na zcela nové výrobní nástroje, které by byly schopny pracovat na podstatně větší ploše. Proto bylo nutné, aby na větší wafery přecházely firmy pokud možno naráz.

Aktuálně jsou čipy vyráběny především na 200mm waferech, s nimiž se spokojilo téměř 60 výrobců a jen 23 společností umí vyrábět i na 300mm wafery. Přední firmy se před řadou let dohodly, že zkusí přejít na 450mm wafery, což by zajistilo více než dvojnásobnou plochu, takže to by jistě bylo zajímavé. Vytvořeno tak bylo konsorcium G405C, kde figurovaly společnosti Intel, Samsung, GlobalFoundries, TSMC a IBM, čili právě ty, o kterých jsme se dnes bavili především.

Společnosti ustanovily pětiletý program, do nějž měly napumpovat dle původních plánů 4,8 miliard dolarů a výsledkem měl být set nástrojů a technologií pro výrobu čipů na 450mm wafery. Tento program ale letos končí a dvě nejmenované firmy toho měly využít ke svému rozhodnutí z projektu vycouvat. Ať už byl důvod jakýkoliv, dnes je zřejmé, že se bude pokračovat na 300mm waferech. S nástupem EUV a procesů, jež budou posunovat křemíkové technologie k samotným hranicím fyzických možností, budou mít výrobci stejně více než dost problémů na to, aby současně s tím řešili i přechod na větší wafery.