Intel: máme 65nm! AMD: máme dual-core!

- Intel: máme 65nm! AMD: máme dual-core!

- Dual-core

70Mbitů, neboli skoro 9MByte rychlé paměti cache (SRAM) na ploše velikosti dnešního procesoru Prescott. Víc než 500 milionů transistorů o velikosti 65nm každý. To je nový rekord v integraci polovodičů.

Před dvěma lety to bylo na stejné ploše 52Mbitů a 330 milionů transistorů velikosti 90nm. Před dvěma lety zabírala šestitransistorová soustava pro jeden logický bit přesně 1 mikrometr čtvereční, dnes je to již jen 0.57 mikrometrů.

Dost bylo rekordů! Co to přinese? Délka transistorového přechodu se z dnešních 50nm zmenší na 35nm, tedy asi o 30 procent.

Tloušťka oxidu ohraničujícího přechod zůstane zachována na současné velikosti 1.2nm, čímž se (alespoň částečně) předejde nárůstům leakage current. Protože transistor bude fyzicky menší, bude mu stačit menší energie na přepnutí. To ve výsledku znamená, že spotřeba transistoru se zmenší. Intel také vylepšil technologii Strained Silicon, která podle něj redukuje leakage current (jiní ale tvrdí, že ho naopak zvyšuje).

A dále... k současným sedmi vrstvám měděných spojů mezi transistory přibyla osmá a, co je ještě důležitější, byla snížena jejich kapacitance - spoje jsou kratší a nově používají low-k dielektrikum. Na spojích tak dochází k menším ztrátám energie, tepelná energie generovaná na spojích je menší.

Zeptal jsem se v Intelu, jaké přesně výsledky lze očekávat: "V porovnání se současnou 90nm technologií nabízí 65nm při stejném proudu čtyřikrát menší leakage current. Transistory vyráběné Intelovou 65nm technologií mají nejlepší charakteristiky výkon / leakage current."

Sleep logika

Intel se také patrně poučil z designu procesoru Pentium M. Nově je totiž zmíněna jako samozřejmost vlastnost nazvaná "Sleep Transistors". O co jde? Před blok transistorů tvořících části cache je přidána další logika, která umožňuje transistor uspávat. Jako odpověď na mojí otázku směřující k tomu, zda vůbec je možné použít takto uspaný blok k uchovávání dat, mi bylo řečeno, že kontrolní logika umožňuje volit rozsah uspání - jedna možnost je ho kompletně odpojit (když není potřeba jeho úložná kapacita), druhá naopak umožňuje s ne tak velkou redukcí spotřeby zachovat data (... a třetí možností je samozřejmě plně operační stav).

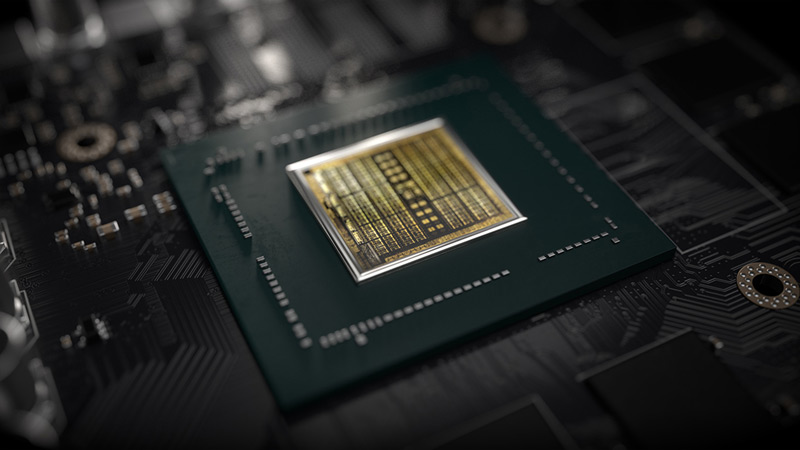

Na snímku výše je vidět, jak s použitím sleep transistorů došlo k redukci leakage. Snímek je z termovize (měří úroveň infračerveného záření), světlejší plochy značí vyšší teplotu, tedy i vyšší spotřebu. Snad jedinou nevýhodou je, že takto je potřeba na stejné množství dat více transistorů, něco je totiž využije na onu logiku - proto 500 milionů / 70Mbit je více než 7 transistorů na jeden bit, zatímco starší přístup 330 milionů / 52Mbit je něco přes 6. Otázkou také je, zda uspávání a probouzení nezvýší latence - a osobně se obávám, že zvýší.

Celkově Intel očekává, že při zvýšení proudu v transistoru se podaří dosáhnout s novou technologií zrychlení přepínání 1.4x. Zda to bude stačit, je otázkou, starší generace nabízely více (vždyť celé jádro Northwood má 1.7x takovou frekvenci jako Willamette), no na druhou stranu že je škálovatelnost v těchto velikostech transistorů prakticky mrtvá, již víme. Osobně spíše doufám v redukci spotřeby proti současnému designu. Dobrou zprávou je, že Intel počítá s první produkční výrobou 65nm procesorů již ke konci příštího roku.

V roce 2007 bude následovat technologie 45nm s přechodem o velikosti pouhých 25nm.