Transmeta Efficeon – útok na pozici Pentia M

20.10.2003, Zdeněk Kabát, článek

Tento týden byl společností Transmeta představen nový procesor pro notebooky, který kromě nízké spotřeby disponuje i efektivní architekturou. A připomíná i Athlon 64 – obsahuje totiž v jádře paměťový řadič a používá HyperTransport.

Kapitoly článku:

- Transmeta Efficeon – útok na pozici Pentia M

- Efektivita a spotřeba

- LongRun, roadmap a závěr

Ti z Vás, kteří znají společnost Transmeta více než od slyšení, jistě vědí, že se proslavila hlavně svým procesorem Crusoe. Tento procesor architektury x86 s instrukcemi VLIW se prosadil na poli malých notebooků, tam kde topící Pentium 4-M či Athlon XP-M neměl šanci. Přestože se neobjevilo příliš řešení s procesorem Crusoe, pokračuje Transmeta ve výrobě procesorů pro tento segment. Novinkou, která byla představena na Microprocessor Forum, je Transmeta Efficeon.

Architektura jádra

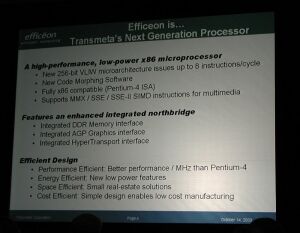

V úvodním odstavci jsem použil zkratku VLIW, která je pro Efficeon velice důležitá. Znamená totiž "Very Long Instruction Word", což je instrukční model použitý např. u procesorů Itanium (ač s jiným cílem). Na rozdíl od hrubé výpočetní síly serverových Itanií slouží VLIW u Efficeonu k rychlejšímu zpracování daného počtu instrukcí. Procesor tedy umí zpracovat až 256-bitová slova za cykl, což znamená třeba osm 32-bitových instrukcí.

Jak vidíte na snímku z prezentace, Efficeon je plně kompatibilní s Pentiem 4 včetně jeho rozšířených sad instrukcí MMX, SSE a SSE2. Co je ale mnohem zajímavější je integrované paměťový řadič, rozhraní pro AGP a řadič sběrnice HyperTransport. Transmeta šla tedy ještě dál než AMD u Athlonu 64 a integrovala do jádra i ovladač AGP, který u architektury HyperTransport systémů zajišťuje standardně AGP tunel.

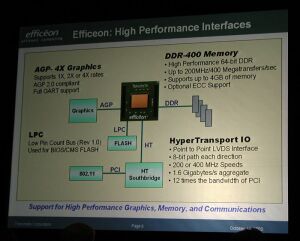

Druhé schéma uvádí zapojení Efficeonu do systému. Zajímavé je, že kromě podpory jednokanálových unbuffered modulů DDR400 je možnost použít i ECC. Rozhraní HyperTransport používá 8-bitovou sběrnici na 200MHz či 400MHz, což ústí v propustnost až 1,6GB/s oběma směry. Pro porovnání - čipsety nForce3 a K8T800 pro Athlon 64 používají pro spojení procesoru s AGP tunelem 16-bitový HyperTransport s přenosy 3,6GB/s, resp. 6,4GB/s.

Dekódování instrukcí pro VLIW

Aby byl Efficeon jakožto procesor s architekturou VLIW plně kompatibilní s instrukcemi x86, je třeba tzv. morfování kódu. Pravda, překlad zní trochu neohrabaně, ale princip je jednoduchý. Ve firmwaru procesoru je obsažen překladač, který převádí x86 instrukce na VLIW tak, aby využití bylo co nejefektivnější.

Změna kódu je prováděna softwarově a nový přeložený kód se cachuje. Software, který překlad zajišťuje, pak podle frekvence používání toho či onoho programu optimalizuje uložený VLIW kód, což má za důsledek, že nejčastěji používané programy jsou nejlépe uzpůsobeny pro Efficeon. Morfování kódu má několik stupňů, jak ukazují následující slidy:

Sám nejsem do architektury VLIW zasvěcen natolik, aby dokázal popsat přesně, co jednotlivé stupně znamenají. V každém případě je optimalizování kódu pro Efficeon, který obsahuje jen 6-stupňovou pipeline, téměř nezbytné (přeci jen Pentium 4 s jeho desítkami stupňů je o něco jinde). Poslední verze CMS (code-morphing software) podporuje i spekulativní zpracování, které dokáže jednoduše obnovit předchozí stav.

Architektura jádra

V úvodním odstavci jsem použil zkratku VLIW, která je pro Efficeon velice důležitá. Znamená totiž "Very Long Instruction Word", což je instrukční model použitý např. u procesorů Itanium (ač s jiným cílem). Na rozdíl od hrubé výpočetní síly serverových Itanií slouží VLIW u Efficeonu k rychlejšímu zpracování daného počtu instrukcí. Procesor tedy umí zpracovat až 256-bitová slova za cykl, což znamená třeba osm 32-bitových instrukcí.

Jak vidíte na snímku z prezentace, Efficeon je plně kompatibilní s Pentiem 4 včetně jeho rozšířených sad instrukcí MMX, SSE a SSE2. Co je ale mnohem zajímavější je integrované paměťový řadič, rozhraní pro AGP a řadič sběrnice HyperTransport. Transmeta šla tedy ještě dál než AMD u Athlonu 64 a integrovala do jádra i ovladač AGP, který u architektury HyperTransport systémů zajišťuje standardně AGP tunel.

Druhé schéma uvádí zapojení Efficeonu do systému. Zajímavé je, že kromě podpory jednokanálových unbuffered modulů DDR400 je možnost použít i ECC. Rozhraní HyperTransport používá 8-bitovou sběrnici na 200MHz či 400MHz, což ústí v propustnost až 1,6GB/s oběma směry. Pro porovnání - čipsety nForce3 a K8T800 pro Athlon 64 používají pro spojení procesoru s AGP tunelem 16-bitový HyperTransport s přenosy 3,6GB/s, resp. 6,4GB/s.

Dekódování instrukcí pro VLIW

Aby byl Efficeon jakožto procesor s architekturou VLIW plně kompatibilní s instrukcemi x86, je třeba tzv. morfování kódu. Pravda, překlad zní trochu neohrabaně, ale princip je jednoduchý. Ve firmwaru procesoru je obsažen překladač, který převádí x86 instrukce na VLIW tak, aby využití bylo co nejefektivnější.

Změna kódu je prováděna softwarově a nový přeložený kód se cachuje. Software, který překlad zajišťuje, pak podle frekvence používání toho či onoho programu optimalizuje uložený VLIW kód, což má za důsledek, že nejčastěji používané programy jsou nejlépe uzpůsobeny pro Efficeon. Morfování kódu má několik stupňů, jak ukazují následující slidy:

Sám nejsem do architektury VLIW zasvěcen natolik, aby dokázal popsat přesně, co jednotlivé stupně znamenají. V každém případě je optimalizování kódu pro Efficeon, který obsahuje jen 6-stupňovou pipeline, téměř nezbytné (přeci jen Pentium 4 s jeho desítkami stupňů je o něco jinde). Poslední verze CMS (code-morphing software) podporuje i spekulativní zpracování, které dokáže jednoduše obnovit předchozí stav.