Common Platform, sdružení třech velkých firem vyrábějících počítačové a jiné čipy, uspořádalo akci Technology Forum, kde bylo přijato usnesení o přechodu na 14nm výrobní technologii využívající tranzistory FinFET 3D (Fin Field Effect Transistor). Jedná se o firmy IBM, Samsung a Global Foundries, k níž má blízko také společnost AMD, která o tranzistorech FinFET a jejich vývoji hovořila již před deseti lety. Čipy založené na FinFET 3D budou bezpochyby reakcí na Tri-Gate tranzistory, jež Intel s velkou pompou představil před necelým rokem. První 14nm čipy z tranzistorů FinFET 3D by měly být vyrobeny v roce 2014 nebo 2015 a zkombinovány s Fully Depleted Silicon-On-Insulator (FD-SOI) pro dosažení vysoké hustoty a potřeby nízkého napětí, to v porovnání s možnostmi technologie Partially-Depleted Silicon-On-Insulator (PD-SOI), která se blíží svým limitům. Poslední informace hovoří o možnosti vrstvení čipů na sebe, což přinese jednu velkou výhodu - zmenšení jejich celkové plochy. Z

Common Platform, sdružení třech velkých firem vyrábějících počítačové a jiné čipy, uspořádalo akci Technology Forum, kde bylo přijato usnesení o přechodu na 14nm výrobní technologii využívající tranzistory FinFET 3D (Fin Field Effect Transistor). Jedná se o firmy IBM, Samsung a Global Foundries, k níž má blízko také společnost AMD, která o tranzistorech FinFET a jejich vývoji hovořila již

.

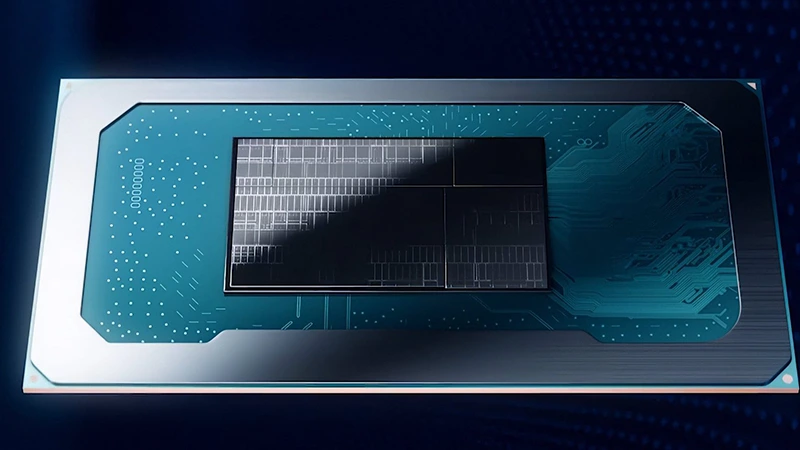

Čipy založené na FinFET 3D budou bezpochyby reakcí na Tri-Gate tranzistory, jež Intel s velkou pompou

před necelým rokem. První 14nm čipy z tranzistorů FinFET 3D by měly být vyrobeny v roce 2014 nebo 2015 a zkombinovány s Fully Depleted Silicon-On-Insulator (FD-SOI) pro dosažení vysoké hustoty a potřeby nízkého napětí, to v porovnání s možnostmi technologie Partially-Depleted Silicon-On-Insulator (PD-SOI), která se blíží svým limitům.

Poslední informace hovoří o možnosti vrstvení čipů na sebe, což přinese jednu velkou výhodu - zmenšení jejich celkové plochy.

Zdroj: