Seznam kapitol

V dnešním článku zaměřeném na výrobní technologie se vrátíme k technologii SOI a podíváme se, kam se ubírá její vývoj v posledních letech. Potom si také uvedeme novinky v oblasti moderních výrobních technologií používaných v polovodičovém průmyslu...

Novinky a překážky současné fotolitografie

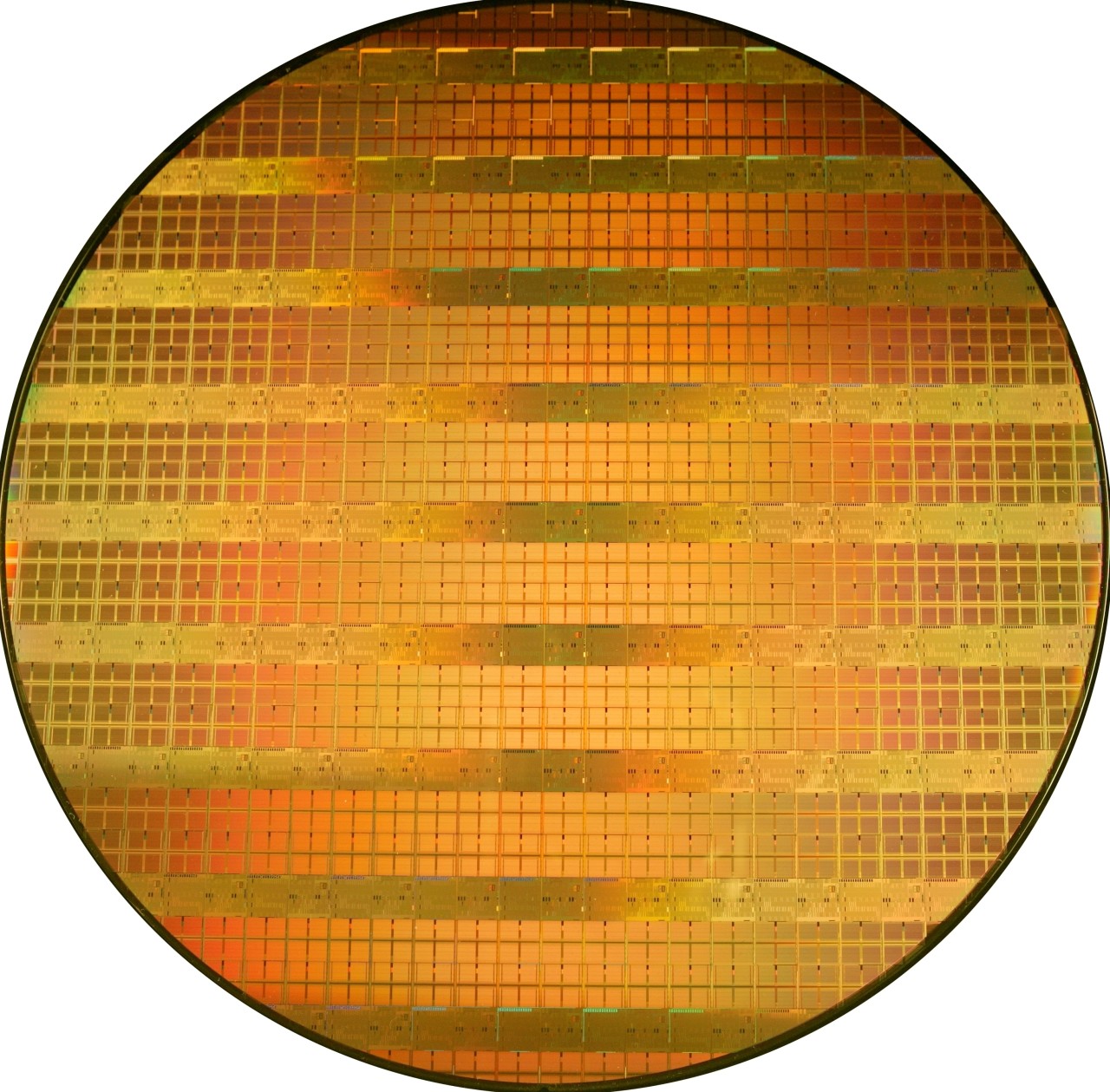

Stále větším problémem je vytváření stále menších a menších struktur na waferu pomocí fotolitografie, která provází vznik každého čipu. Proces osvícení waferu přes fotolitografickou masku a vznik stále jemnějších struktur naráží na limity použitého záření, a to stále ještě s vlnovou délkou 193 nm. Jak funguje současná "suchá" a imerzní fotolitografie, i její základní problémy, jsem podrobněji popsal v článku

Jak vzniká procesor - moderní výrobní technologie

, případně ve volném pokračování článku

Moderní výrobní technologie II

, který se fotolitografii také věnuje.

V každém případě si zde dovolím menší rekapitulaci a doplnění informací tak, jak ji shrnuje například ITRS (International Technology Roadmap for Semiconductors). Ta je obvykle výchozím bodem při řešení potíží současného polovodičového průmyslu a je tímto odvětvím také akceptována. S očekáváním příchodu 32 nm již polovodičový průmysl řeší, jak udržet stále rychlý sled dalších výrobních procesů. Technologie pro komerční nasazení 16nm technologie jsou bez EUV litografie v současné době neřešitelným oříškem.

Na 32 nm nebude problém dosáhnout i se současnou technologií pomocí imerzní fotolitografie a metod dvojité expozice - s vhodným fotorezistem, vhodnou kapalinou (která vyplní prostor mezi optikou fotolitografického zařizení a waferem) a optimalizací výrobních postupů. Pro 22nm výrobní technologii je ve hře další generace imerzní fotolitografie označovaná jako 193i+ (s použitím nových materiálů pro optiku a nutné změny kapalin a fotorezistu), protože podle posledních tvrzení představitelů Intelu, včetně Garry Pattona, EUV zřejmě nebude připravená ani pro blížících se 22 nm. Nutné změny přinese několik metod na zvýšení rozlišení současné litografie.

Metody "Double Exposure", "Double Patterning" a "Spacer double patterning" budou hrát u nadcházející generací 32 a 22 nm zásadní roli, a budou držet 193nm fotolitografii při životě. Jednotlivé metody mají samozřejmě své výhody. Ve všech případech ale narůstá cena a klesá výstup ve počtu zpracovaných waferů WPH (Wafers Per Hour, počet ozářených waferů za hodinu) a počet defektů. Double Exposure přináší nutnost použít 2 fotolitografické masky, ale odpadá opětovné vyvolání a znovunanášení fotoresistu, jako je tomu u metody Double Patterning. Spacer double patterning používá jedinou fotolitografickou masku a "přidané rozlišení" vzniká oddělením jednotlivých vzorů po prvním leptání, nanesením oxidu, vyhlazení waferu pomocí CMP a následné doleptáním všech nadbytečných horních vrstev. Použití vícenásobného osvitu a více fotolitografických masek v každém případě zdražuje výrobu, a proto se výrobci snaží použití těchto technik minimalizovat.

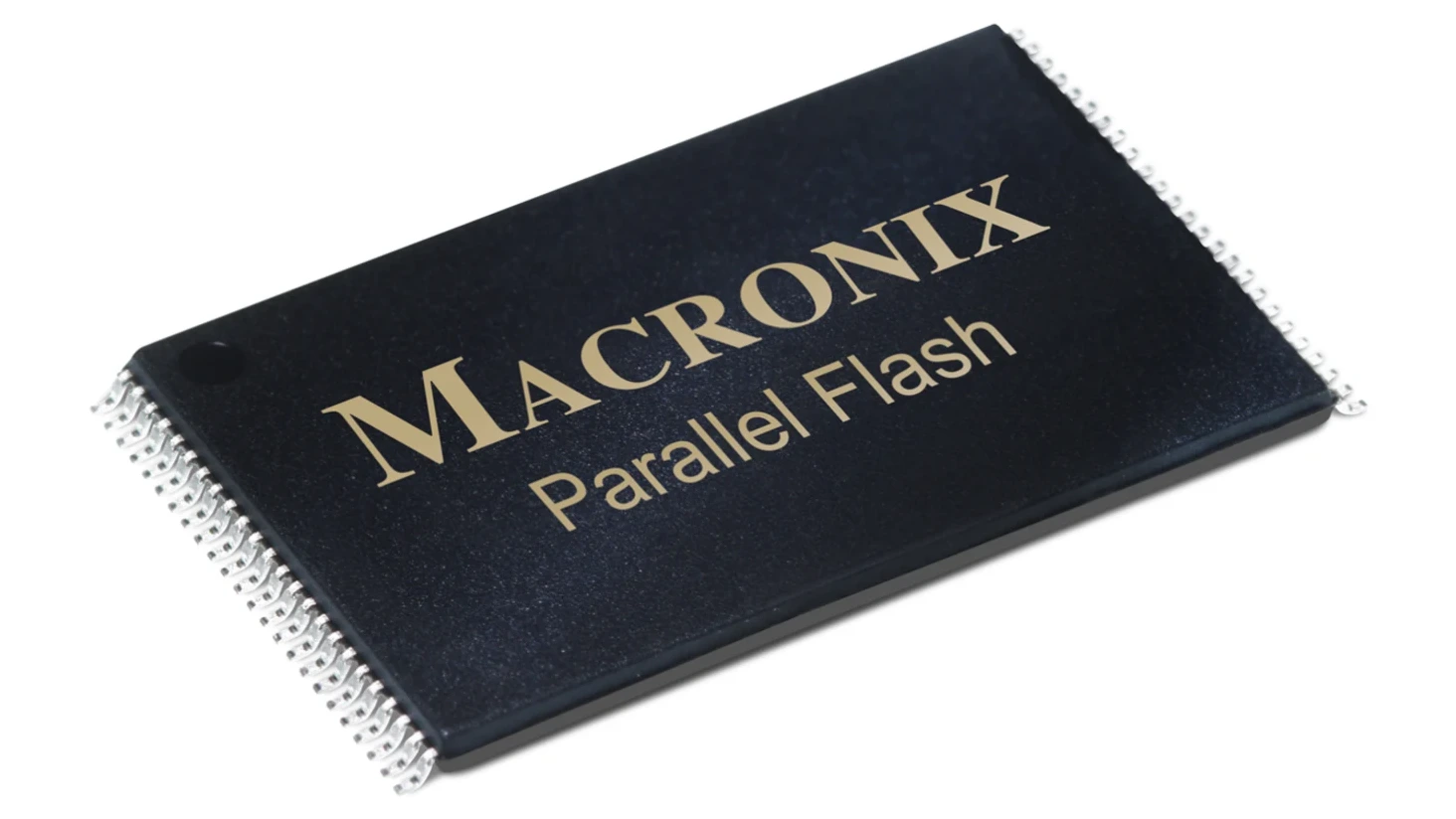

Mezi další možnosti patří již dříve zmíněné technologie nanotisku (IL Imprint) nebo ML2. To nikdy nebude patřit k "trhačům asfaltu" a velice nízký výstup je předurčuje jen pro nasazení pro nízko-sériovou výrobu. Jjedním z možných nasazení jsou ASIC (Application Specific Integrated Circuit) čipy, které do tohoto segmentu dobře zapadají. Experimentální výsledky zatím ukazují výstup mezi 10

-2

-10

-1 s

s možným zvýšením až na 1 WPH a v případě použití masivní paralelizace osvitu waferu až na úrověň 10 WPH. Oproti současným řešením 193nm DUV a DUVi s výkonem přes 100 až 175 WPH samozřejmě není ML2 skutečnou konkurencí. Výhodou jsou nicméně odpadlé náklady na sadu fotolitografických masek (které se v současnosti pro 45 nm mohou vyšplhat i přes 3 miliony dolarů) a také možnost prakticky okamžité tvorby prototypů a testovacích čipů.

PML2 jako "bezmaská" litografie - používá přímé ozařování waferu, zdroj: SPIE, RIMANA

Vzhledem ke zlomku investice oproti EUV jsou dosavadní výsledky PML2 litografie přesvědčivé (vytvořené linky i s použitím současných fotorezistů jsou pod úrovní 22 nm) - největším nedostatkem PML je bohužel velice nízký výstup WPH, zdroj: SPIE

Jediným v současnosti zvažovaným řešením pro skutečně "masovou" výrobu čipů je tedy EUV. EUV litografie by mohla efektivně vyřešit alespoň 3 následující generace výrobních procesů.

Kdy přijde EUV?

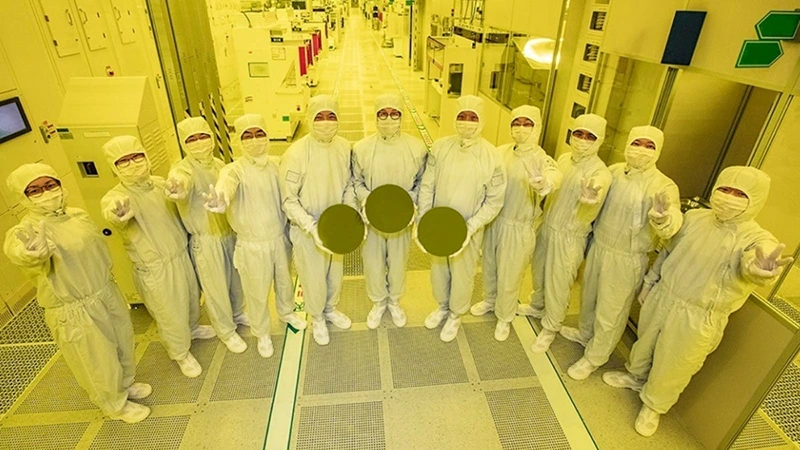

Pokud se ohlédneme pár roků nazpět, právě EUV nám může ukázat, jak velké bariéry v nasazení nových technologií je občas třeba překonat. Nasazení EUV již bylo několikrát odloženo (s EUV se dříve počítalo dokonce i pro 45nm proces) a situace nebude jiná ani v případě 32nm výrobní technologie, která nás v optimálním případě čeká již koncem tohoto roku. Řada testovacích čipů vytvořená EUV litografií je také již na světě, ale ke komerčnímu nasazení technologie stále není připravena. Jak ostatně tvrdí Garry Patton, technologie EUV zřejmě nebude připravená ani pro 22 nm a stejné názory panují i v IBM.

IMEC EUV ADT (Alpha Demo Tool) a výsledky s počtem ozářených waferů (produkční zařízení mají metu > 100 WPH), zdroj: IMEC

Poměrně optimisticky se k EUV staví ASML jako výrobce fotolitografických zařízení a již na začátek roku 2010 připravuje předprodukční EUV kity (předpokládaný je výkon okolo 60 WPH s možností rozšíření až k 100 WPH).

Roadmapa nasazení EUV podle ASML, zdroj: ASML

I zde se ovšem jedná spíše o předpoklad, a kvůli celkovému poklesu v IC odvětví, které výrazně zasáhlo bez výjimek všechny firmy na trhu, může dojít k pozdržení EUV a tak i 16 nm technologie. Jiné metody masového zpracování waferů, tak jak je má umožnit EUV, nejsou v současnosti známy. Výsledky EUV se samozřejmě stále zlepšují, ale i tak je zde řada nedořešených problémů. Kromě nedostatečného výstupu je to zejména degradace litografických masek a potíže vytvořit masku bez defektů a pro komerční produkci zatím nevhodné fotorezisty...

EUV samotná samozřejmě nebude řešením pro "všechny", zejména kvůli ceně. Nebude to ani řešení pro všechny vrstvy čipu, ale pouze pro kritické části a bude vydatně kombinována s DUVi. AMD zatím také míří s EUV k metě 16 nm. Podle současných předpokladů AMD nasadí EUV s 16nm technologií až pro 5 kritických vrstev čipu (M1 až M5, včetně mezispojů), kombinaci s DUVi během roku 2014. K EUV s 16 nm zamíří samozřejmě i IBM, Intel a řada dalších velikánů. Pojďme si tedy shrnout, co nás čeká a nemine.