Společnost Intel a jeho Altera se pochlubila světově prvním čipem typu SIP (System in Package), který obsahuje paměti HBM2 a integrované SoC a FPGA čipy Stratix 10. Co se pod tím vším skrývá?

Zrovna včera jsme mluvili o společnostech

, které uzavřely partnerství ve snaze obohatit architekturu IBM Power o vysoce specializovaná FPGA Xilinx, která budou v určitých úlohách poskytovat potřebný výkon. IBM chce s pomocí tohoto řešení zaútočit právě na Intel, ovšem ten má v rukávu svou nedávno akvizovanou Alteru, s jejíž pomocí představil také své řešení založené rovněž i na FPGA čipech.

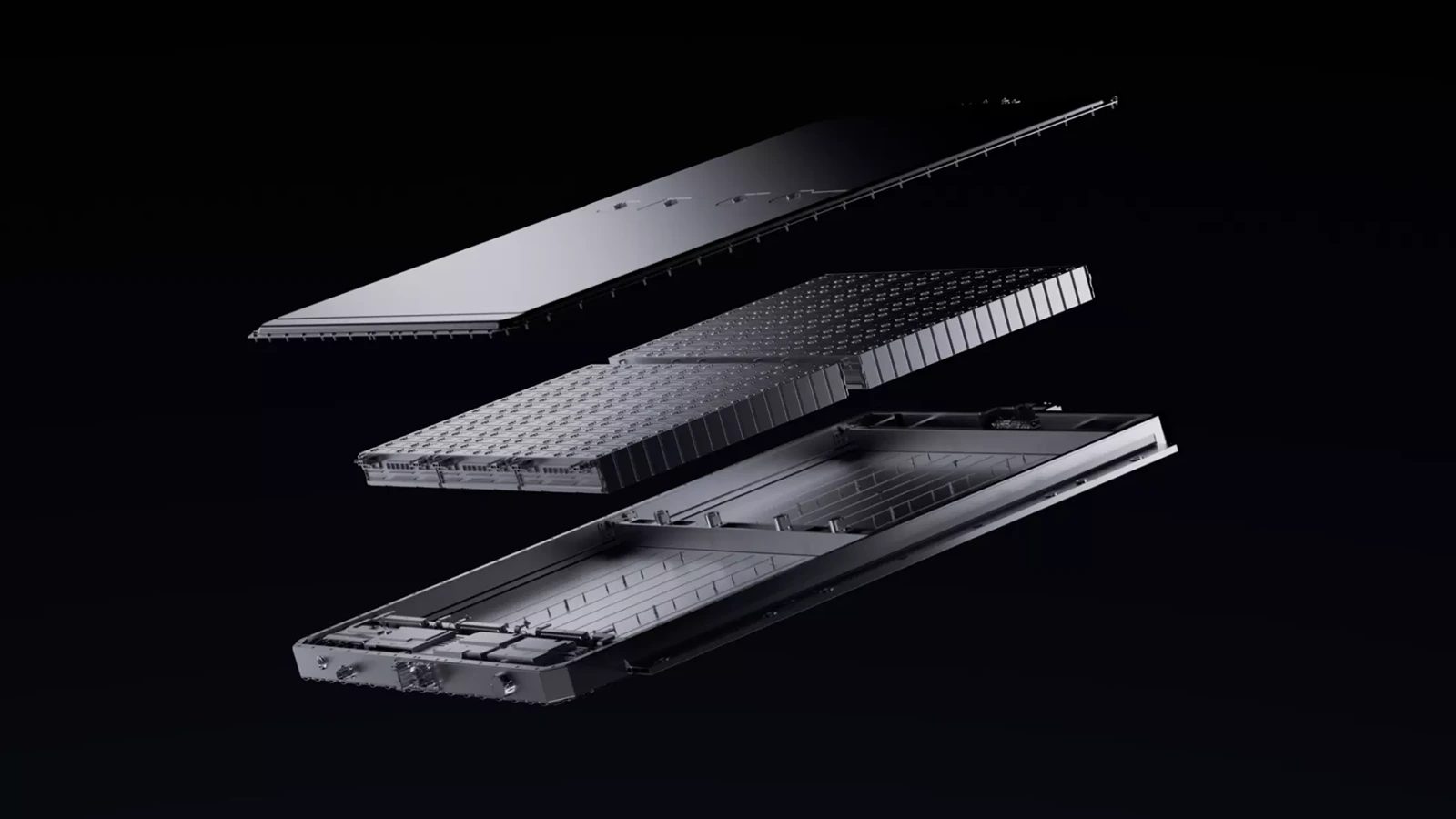

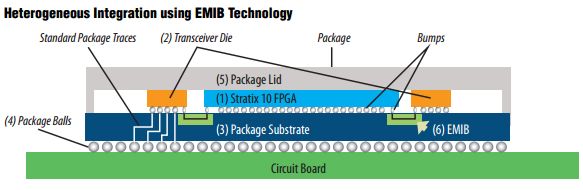

Intel mluví o architektuře HyperFlex a konkrétně o prvním Stratix 10 FPGA zařízení typu SIP s integrovanými paměťmi HBM2. Na ty se těšíme především jako na součást nové generace grafických karet, ale už dříve bylo zřejmé, že tento typ pamětí bude využit i jinak. Tkví totiž v nich velký potenciál díky jejich dobře škálovatelné kapacitě, výkonu a vysoké energetické efektivitě díky využití velice širokého rozhraní, díky čemuž HBM nemusí (alespoň zatím) pracovat na vysokých frekvencích. V tomto případě Intel využil pro propojení všech částí své rozhraní EMIB (Embedded Multi-die Interconnect Bridge), což je něco podobného jako křemíkový "interposer" spojující čipy AMD Fiji s HBM. EMIB je 2.5D zařízení, čili obsahuje datové spoje ve více vrstvách s využitím známých TSV (Through-Silicon Via), tedy vertikálních spojů propojujících zmíněné vrstvy. Asi nejlépe to ukazuje následující obrázek:

Čipy FPGA (Field Programmable Gate Arrays) mají tu výhodu, že jsou programovatelné, a tudíž mají vysokou flexibilitu, aby se mohly úzce orientovat na různé výpočetní úlohy. Ve spojení s rychlými HBM2 pak může jít ve výsledku o dosud nevídaně výkonné integrované řešení. To může být dle Altery využito pro strojové učení, rozpoznávání obrazových dat i zpracování velkých objemů dat nebo zpracování videa ve vysokých rozlišeních (8K). Firma se také chlubí, že v současné době její Stratix 10 DRAM SiP nemá mezi programovatelnými FPGA konkurenci.

Za zmínku také stojí, že něco podobného by si měla

připravovat také společnost AMD

, ovšem nic konkrétního jsme od ní zatím neslyšeli. Čili by se dalo uvažovat o tom, že AMD plánuje spojení architektury Zen, programovatelných FPGA a pamětí HBM, ale zatím je velká otázka, zda se něco takového opravdu objeví. Uvidíme tedy, zda AMD bude mít na trhu srovnatelné řešení jako Intel s Alterou, jejichž Stratix 10 SiP HBM2 má přijít na trh možná už v příštím roce. A to AMD s největší pravděpodobností nestihne.

Zdroj: