Seznam kapitol

V našem článku se tentokráte podíváme na to, co pro nás chystá Intel u další generace své procesorové architektury Haswell. Společnost nám odtajnila na IDF 2012 některé zajímavé detaily a plány pro novou procesorovou rodinu.

Systém vyrovnávacích pamětí

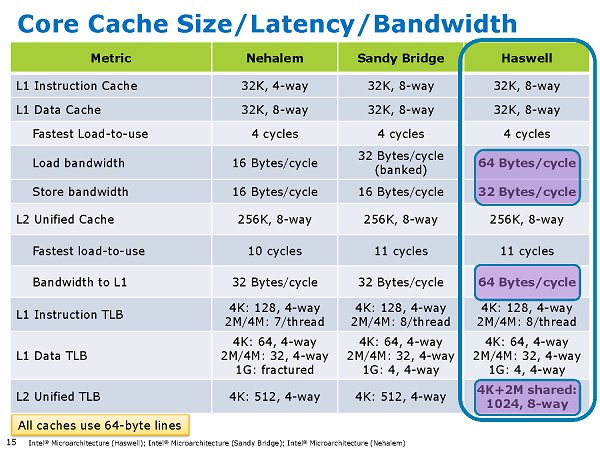

Pokud jsme si uvedli, že Haswell má teoreticky dvojnásobný výpočetní výkon, tak je to také úzce spjato s tím, že výpočetní jednotky je potřeba „krmit“. Intel musel tedy optimalizovat také na straně vyrovnávacích pamětí architektury (cache). Velikost a uspořádání cache zůstaly stejné, ale razantně se zvýšila propustnost k vyrovnávacím pamětem. Rychlost cache je u Haswellu adekvátní rychlosti zpracování rychlosti vykonávání instrukcí AVX2. Porty pro čtení/zápis jsou v případě L1 cache Haswell 32 bytů s 256bitovou šířkou. Haswell zvladá 2 přečtení a 1 zápis od cache za takt. Celkově má L1 cache dvojnásobnou propustnost a podstatně nižší latenci.

Pokud jsme hovořili od L1 cache, tak musíme také zmínit L2 cache, která je sice větší než L1 cache, ale je oproti ní pomalejší. Intel ale L2 udělal v případě Haswellu širší, takže nyní může přijmout až 64 bytů dat za takt, což je opět dvojnásobek toho, co dokáže Ivy Bridge/Sandy Bridge. Výkonnost cache L2 se zvýšila skrze propustnost, latence zůstala stejná jako u předchozích architektur. Intel prozatím nehovoří o velikosti nebo rychlosti L3 cache.

Je velmi pravděpodobné, že velikost L3 cache bude odvislá od počtu fyzických jader v procesoru. Z praxe je jasné, že více jader bude znamenat větší cache a naopak. V případě interní struktury zde nejsou žádné podstatné změny a máme zde také klasickou Ring Bus, kterou známe z Ivy Bridge/Sandy Bridge architektur. Intel slibuje také optimalizaci paměťového řadiče, který by měl nově garantovat větší rychlost zápisu.

TSX (Transactional Synchronization Extensions)

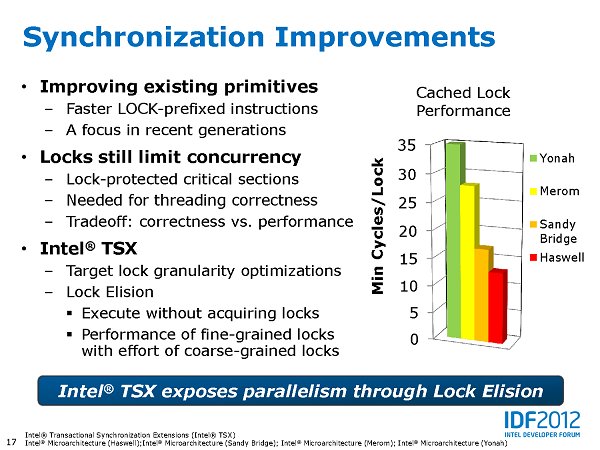

Krom všude omílaného AVX2, respektive nového instrukčního setu v architektuře Haswell, je zde také TSX (Transactional Synchronization Extensions), která přidává hardwarovou transakční paměťovou podporu. Pro Intel je stěžejní, aby vývojáři měli snadnou cestu k psaní paralelního kódu. TSX disponuje dvěma softwarovými rozhraními pro vymezení oblasti kódu určeného ke zpracování. Hardware Lock Elision je instrukční rozhraní určené ke zpětné kompatibilitě s hardware bez jednotky TSX, takže všem starším architekturám Ivy Bridge/Sandy Bridge a dalším.

Druhé rozhraní RTM (Restricted Transaction Memory) poskytuje programátorům větší flexibilitu s využitím nového instrukčního setu. TSX hardwarově monitoruje množství vláken a přístupy k paměti, je schopno zrušit nebo pozastavit transakce, které nemohou být v daném momentu úspěšně dokončeny.