Seznam kapitol

V dnešním článku se zaměříme na technologii vrstvení čipů a integrovaných obvodů, na tak zvaný "stacking". Protože se jedná o perspektivní technologii, která se bude více a více používat, podíváme se na ni dnes trochu podrobněji.

Pohled na technologii stackingu čipů

Na technolgoii 3D stackingu již léta pracuje řada firem a výzkumných pracovišť. Kromě těch největších, jako jsou například IBM, Intel, Samsung přes Toshibu a řadu dalších společností, i centra a výzkumná střediska jako například RTI International nebo IMEC a Amkor Technology. Mimochodem, právě IMEC a Amkor Technology nedávno podepsali dohodu o spolupráci na 3D integraci čipů s výrobní technologií pod 32 nm s použitím imerzní fotolitografie založené na 193nm vlnové délce a také EUV litografii.

Vrstvení se týká, jak již bylo zmíněno, i mezispojů. Na technologii zlepšení mezispojů pro 3D stacking také pracuje řada firem a společností, mezi nimiž můžeme jmenovat například Evropský výzkumný institut CEA-Leti-Minatec (Grenoble, Francie) a Alcatel Micro Machining Systems (Annecy, Francie), které v současné době již spolupracují na technologii micro-spojů, jež dovolí používat síť mezispojů s vysokou hustotou na obou stranách čipu. Mezispoje na této úrovni mohou dosáhnout i hodnot okolo deseti tisíc na mm2. To vše za použití výrobních postupů v LTPECVD (technologii plazmové depozice plynné fázi za nízkých teplot), která má přinést dostupnost této technologie i pro průmyslové nasazení.

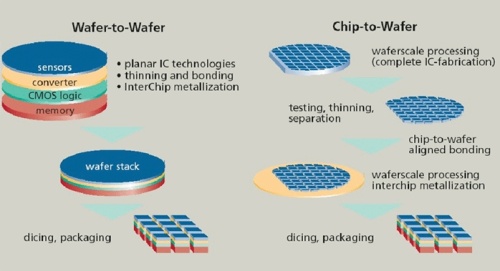

Ačkoliv se tedy může zdát, že v popředí tohoto výzkumu jsou zejména společnosti zabývající se pouze výrobou mikroprocesorů, opak je pravdou. Na těchto technologiích spolupracuje i řada firem, které se zabývají například senzory nebo dalším průmyslovým využitím těchto technik pro elektronická zařízení. Z hlediska principu spojování čipů můžeme technologii vrstvení rozdělit na několik kategorií. Asi nejzákladnější je rozdělení technologie spojení čipu a IC na technologie: wafer - wafer, čip - wafer nebo čip - čip.

Vertikální integrace a metody wafer-wafer a čip-wafer, zdoj: Infineon

Překlad je to možná mírně neumělý, ale výstižný - přesně vystihuje, "o co jde". Jak se tyto technologie liší? A která je lepší? Odpověď samozřejmě není tak jednoduchá a obě mají svá pro i proti. Při spojení

wafer - wafer

dochází ke spojení celých waferů, při spojení

čip - wafer

se vždy spojí již konkrétní čip s waferem, kde jsou již vytvořeny další struktury a konečně při spojení

čip na čip

se vrství již konkrétní "hotová" jádra. Je nasnadě, že tyto metody mají své výhody i nevýhody, at již z hlediska ceny nebo výtěžnosti, složitosti a náročnosti na výrobní technologii. Spojování celých waferů má samozřejmě větší výstup WPH (Wafers Per Hour - počet zpracovaných waferů za hodinu), zatímco spojení čip na čip klade nejnižší nároky na výrobní technologii.

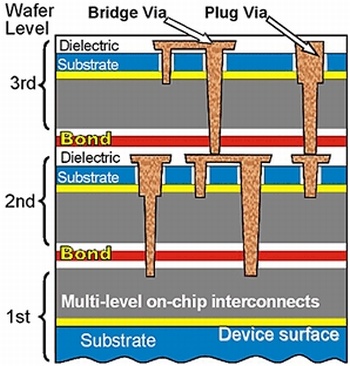

Schéma spojení několika vrstev z hlediska waferů, zdroj: RPI

Ke spojování a při výrobě vrstvení čipů se používá technologie TSV (Through-Silicon Via), což je metoda spojení jednotlivých waferů, respektive čipů, pomocí vodivých spojení (vedených skrz wafer nebo čip). I zde je samozřejmě metod jak spojit wafery, respektive čipy, více - mají se vytvořit vodivá spojení "vias" při vytváření a formování struktur na waferu nebo při zapouzdřování?

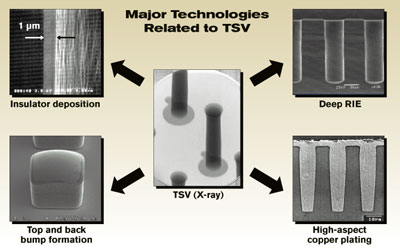

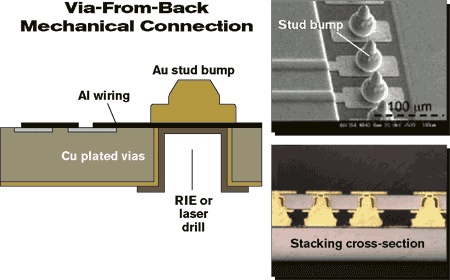

Technologie TSV pro vytvoření mezispojů mezi vrstvami ICs jako například "deep trench RIE" nebo"laser drilling" a následné plnění mezispojů a vytváření kontaktů, zdroj: S. Denda, Nagano Prefectural Institute of Technology

Možností je několik, například pomocí microlaseru nebo pomocí technologie DRIE (Deep Reactive-Ion Etching) a následného vodivého vyplnění "miniotvorů". Pomocí DRIE se také například vytváří otvory pro kondenzátory v DRAM. K následnému spojení se používá také několik technologií, jednou z nich je například níže uvedená metoda od Hitachi.

Zde jsou na vrchu čipu pomocí zlata vytvořeny kontakty, které jsou následně dolní stranou (dálší částí čipu) protlačeny kontakty (částí čipu s otvory), zdroj: Hitachi